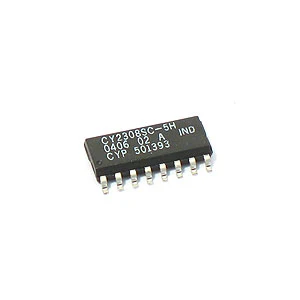

A20546 - CY2308SC-5HT 3.3V Zero Delay Buffer (Cypress)

The CY2308SC-5HT PLL enters a power down state when there are no rising edges on the REF input. In this mode, all outputs are three-stated and the PLL is turned off resulting in less than 50 ?A of current draw. Multiple CY2308SC-5HT devices accept the same input clock and distribute it in a system. In this case, the skew between the outputs of two devices is less than 700 ps. The CY2308SC-5HT is a high drive version with REF/2 on both banks.

Features:

Zero input-output propagation delay, adjustable by capacitive load on FBK input

Multiple configurations

Multiple low skew outputs

Two banks of four outputs, three-stateable by two select inputs

10 MHz to 133 MHz operating range

75 ps typical cycle-to-cycle jitter (15 pF, 66 MHz)

3.3V operation

Datasheet Available:Cypress Semi CY2308SC-5HT

SOIC 16 package. Manufactured by Cypress Semiconductor.

A20546

Description

The CY2308SC-5HT PLL enters a power down state when there are no rising edges on the REF input. In this mode, all outputs are three-stated and the PLL is turned off resulting in less than 50 ?A of current draw. Multiple CY2308SC-5HT devices accept the same input clock and distribute it in a system. In this case, the skew between the outputs of two devices is less than 700 ps. The CY2308SC-5HT is a high drive version with REF/2 on both banks.

Features:

Zero input-output propagation delay, adjustable by capacitive load on FBK input

Multiple configurations

Multiple low skew outputs

Two banks of four outputs, three-stateable by two select inputs

10 MHz to 133 MHz operating range

75 ps typical cycle-to-cycle jitter (15 pF, 66 MHz)

3.3V operation

Datasheet Available:Cypress Semi CY2308SC-5HT

SOIC 16 package. Manufactured by Cypress Semiconductor.

A20546