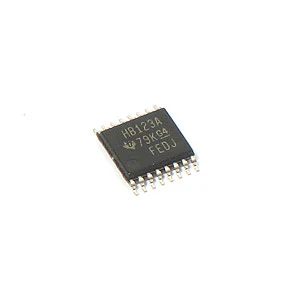

A20571S - SN74AHCT123APWR SMD Dual Retriggerable Multivibrator (TI)

Pulse triggering occurs at a particular voltage level and is not directly related to the transition time of the input pulse. The A\, B, and CLR\ inputs have Schmitt triggers with sufficient hysteresis to handle slow input transition rates with jitter-free triggering at the outputs.

Once triggered, the basic pulse duration can be extended by retriggering the gated low-level-active (A\) or high-level-active (B) input. Pulse duration can be reduced by taking CLR\ low. CLR\ input can be used to override A\ or B inputs. The variance in output pulse duration from device to device typically is less than ?0.5% for given external timing components. During power up, Q outputs are in the low state, and Q\ outputs are in the high state. The outputs are glitch free, without applying a reset pulse.

Features:

Inputs Are TTL-Voltage Compatible

Schmitt-Trigger Circuitry On A\, B, and CLR\ Inputs for Slow Input Transition Rates

Edge Triggered From Active-High or Active-Low Gated Logic Inputs

Retriggerable for Very Long Output Pulses

Overriding Clear Terminates Output Pulse

TSSOP 16 package. Manufactured by Texas Instruments.

A20571S

Description

Pulse triggering occurs at a particular voltage level and is not directly related to the transition time of the input pulse. The A\, B, and CLR\ inputs have Schmitt triggers with sufficient hysteresis to handle slow input transition rates with jitter-free triggering at the outputs.

Once triggered, the basic pulse duration can be extended by retriggering the gated low-level-active (A\) or high-level-active (B) input. Pulse duration can be reduced by taking CLR\ low. CLR\ input can be used to override A\ or B inputs. The variance in output pulse duration from device to device typically is less than ?0.5% for given external timing components. During power up, Q outputs are in the low state, and Q\ outputs are in the high state. The outputs are glitch free, without applying a reset pulse.

Features:

Inputs Are TTL-Voltage Compatible

Schmitt-Trigger Circuitry On A\, B, and CLR\ Inputs for Slow Input Transition Rates

Edge Triggered From Active-High or Active-Low Gated Logic Inputs

Retriggerable for Very Long Output Pulses

Overriding Clear Terminates Output Pulse

TSSOP 16 package. Manufactured by Texas Instruments.

A20571S