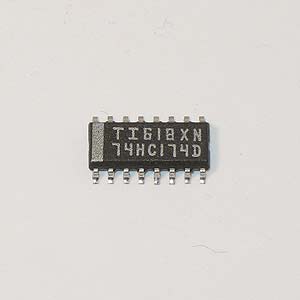

G353S - 74HC174 SMD Hex D-Type Flip-Flop with Reset

The register is fully edge-triggered. The state of each Dinput, one set-up time prior to the LOW-to-HIGH clocktransition, is transferred to the corresponding output of the flip-flop. A LOW level on the MR input forces all outputs LOW, independently of clock or data inputs.The device is useful for applications requiring true outputs only and clock and master reset inputs that are common to all storage elements.

Features:

Six edge-triggered D-type flip-flops

Asynchronous master reset

Output capability: standard

ICC category: MSI

SOIC 16 package. Actual brand may vary from picture.

G353S

Description

The register is fully edge-triggered. The state of each Dinput, one set-up time prior to the LOW-to-HIGH clocktransition, is transferred to the corresponding output of the flip-flop. A LOW level on the MR input forces all outputs LOW, independently of clock or data inputs.The device is useful for applications requiring true outputs only and clock and master reset inputs that are common to all storage elements.

Features:

Six edge-triggered D-type flip-flops

Asynchronous master reset

Output capability: standard

ICC category: MSI

SOIC 16 package. Actual brand may vary from picture.

G353S